PCI Express

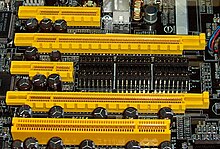

Il PCI Express (Peripheral Component Interconnect Express), abbreviato in PCIe, è uno standard di interfaccia d'espansione a bus seriale per computer ad alta velocità, progettato per sostituire i vecchi standard PCI, PCI-X e AGP.

È basato su un trasferimento dei dati seriale, a differenza di quello parallelo del PCI, che semplifica il layout del PCB delle schede madri ed è costituito da una serie di canali. Ciò consente una notevole modularità, in quanto possono essere aggregati più canali per aumentare la banda passante disponibile o per supportare particolari configurazioni, come ad esempio l'utilizzo di due o più schede video; inoltre la larghezza di banda di ciascun canale è indipendente da quella degli altri.

Le specifiche e regolamentazioni sono mantenute e sviluppate da PCI-SIG (PCI Special Interest Group).

Versioni

modificaPCI Express 1.0

modificaPCI Express è stato progettato per sostenere il sempre maggior fabbisogno energetico delle schede video di ultima generazione. Infatti, a differenza dello slot AGP, in grado di erogare un massimo di 50 watt, la revisione 1.x di PCI-ex supporta carichi fino a 75 W, permettendo così di eliminare il connettore Molex dalle schede di fascia media e medio-bassa anche se è rimasto per tutte le altre.

Queste porte prodotte dalla Intel e che hanno debuttato nel 2003, presentano una larghezza di banda in 1x di 250 MB/s (o 4 GB/s in modalità 16x) ed una velocità di trasferimento x1 di 2,5 GT/s (Giga Transfer al secondo).

PCI Express 2.0

modificala PCI Express 2.0 è l'evoluzione dello standard PCI Express per la connessione di periferiche alla scheda madre presentato il 16 gennaio 2007 è arrivato sul mercato a metà 2007 grazie al supporto dato dal chipset Intel Bearlake nella versione chiamata "X38".

A settembre 2006, Rambus, già famosa per l'introduzione delle memorie RDRAM, aveva in realtà già annunciato la disponibilità dei primi dispositivi di controllo concepiti per la nuova generazione di PCI Express.

Il primo PCIe 2.0 fu lo X38 e la scheda veniva fornita fin dall'ottobre 2007 da vari produttori quali ASUS, Gigabyte.[1]

Caratteristiche tecniche

modificaLa nuova versione di PCI Express raddoppia l'ampiezza di banda (e la velocità di trasferimento) fornita dal PCI Express di prima generazione 1.0, portandola da 250 MB/s (o 2,5 GT/s) a 500 MB/s (o 5 GT/s), sempre in modalità 1x.

Pertanto in modalità 16x si passa dai 4 GB/s del PCIe 1.0 ad 8 GB/s per l'attuale 2.0.

Il PCI Express 2.0 offre slot x1, x4, x8 e x16 analogamente al suo predecessore, ma la frequenza è di 250 MHz contro 100 MHz. Dal punto di vista sia meccanico che elettrico comunque, le piattaforme PCI Express 2.0 sono pienamente retrocompatibili con le precedenti versioni 1.0, non creando quindi problemi in caso di aggiornamenti delle piattaforme contenenti periferiche PCI Express 1.0. È prevista anche l'implementazione di una tecnologia per il controllo degli accessi che, oltre a permettere al software di gestire direttamente il routing dei pacchetti, dovrebbe impedire l'intrusione nella comunicazione dati allo scopo di rubare informazioni.

La nuova generazione risolve anche il problema della fornitura energetica alle schede video che con PCI Express è limitata a 75 W; questo valore è da tempo insufficiente per le schede video di medio-alto livello, tanto che quasi tutte ormai montano un connettore d'alimentazione ausiliario collegato direttamente all'alimentatore per far fronte al fabbisogno energetico.

Inoltre, grazie alla funzione Input-Output Virtualization (IOV), viene semplificata la gestione da parte delle macchine virtuali, ognuna con il proprio sistema operativo, delle periferiche collegate attraverso PCI Express 2.0. Sono già stati testati anche i cavi PCI Express 2.0 che permetteranno alle schede non solo la connessione tramite gli slot "tradizionali" ma anche tramite una cavetteria speciale di rame, con velocità di trasferimento per linea, su al massimo 10 metri, di 2,5 Gbit/s.

PCI Express 3.0

modificaA metà 2007 è stato annunciato lo standard che doveva progressivamente sostituire la versione 2.0 del Bus PCI Express a partire dal 2011. Il 18 novembre 2010 il PCI-SIG ha reso pubbliche le specifiche finali[2]. Tali specifiche prevedono la retrocompatibilità, un nuovo schema di codifica 128b/130b ed un'ampiezza di banda del Bus per singola linea 1x di 985 MB/s (o 8 GT/s) che, in modalità 16x, raggiunge pertanto i 15,75 GB/s (raddoppio delle performance dello standard 2.0).

PCI Express 4.0

modificaUscito durante il 2019 con l'avvento delle schede madri AMD X570 e i processori Ryzen di terza generazione, annunciato l'8 giugno 2017 da parte del PCI-SIG[3].

La larghezza di banda raddoppia ancora, passando a 1.97 GB/s (o 16 GT/s) per singola linea 1x (o 31,5 GB/s con collegamento 16x).

PCI Express 5.0

modificaAnnunciato a gennaio 2019 da parte del PCI-SIG[4], l'uscita era prevista nel corso del 2021. L'ampiezza di banda raddoppia e passa a 3,94 GB/s con un collegamento 1x (o 63 GB/s su 16x), con velocità di trasferimento che passerà a 512 GT/s in modalità 16x.

Nonostante le informazioni provenienti da fonti non ufficiali, non è ancora noto con precisione quando effettivamente uscirà.

Tuttavia Samsung, oltre ad altri produttori, ha recentemente annunciato un nuovo SSD PM1743 per server enterprise che utilizza questa tecnologia.[5]

PCI Express 6.0

modificaLe prime informazioni da parte del PCI-SIG sono state rese note a giugno 2019.[6] L'ampiezza di banda verrà ancora raddoppiata ad 7,56 GB/s su 1x (o 121 GB/s su 16x) e la velocità di trasferimento passerà a 1024 GT/s con un collegamento 16x.

PCI Express 7.0

modificaIl PCI-SIG ha annunciato il 21 giugno 2022 le specifiche per la nuova revisione della specifica prevista per il 2025 che incrementerà la velocità di trasferimento a 15,13 GB/s su singola linea 1x (o 242 GB/s su 16x) e l'ampiezza di banda fino a 2048 GB/s sempre con un collegamento 16x.[7]

Concorrenti

modificaSempre a settembre 2006, Intel aveva annunciato lo sviluppo di una tecnologia simile a PCI Express 2.0, pensata anch'essa come successiva a PCI Express. Si trattava di Geneseo su cui si hanno ancora pochi dettagli, ma che doveva consentire ad Intel di offrire una tecnologia simile alla Torrenza di AMD, per "aprire" il proprio Bus all'utilizzo di co-processori sviluppati da altre case.

Al momento comunque non è ancora chiaro se le due tecnologie potranno integrarsi o coesisteranno in concorrenza, sebbene la prima ipotesi sia la più plausibile dato che Intel fa parte anche del consorzio che ha sviluppato PCI Express 2.0.

Comunque al 2023 è un dato di fatto che l'architettura PCI Express si è ormai ampiamente affermata e diffusa ovunque.

Note

modifica- ^ (EN) Gary Key, Wesley Fink, Intel P35: Intel's Mainstream Chipset Grows Up, AnandTech, 21 maggio 2007. URL consultato il 21 maggio 2007.

- ^ PCI Express 3.0 completato, i prodotti accelerano, su tomshw.it. URL consultato il 21 novembre 2010 (archiviato dall'url originale il 22 novembre 2010).

- ^ Corsini Paolo, Il controller PCI Express 4.0 è la vera novità del chipset AMD X570, su hwupgrade.it, 21 maggio 2019. URL consultato il 2 luglio 2019.

- ^ https://www.hwupgrade.it/news/skvideo/doppia-bandwidth-per-lo-standard-pcie-50-al-debutto-tra-1-anno_80248.html

- ^ (EN) Samsung Develops High-Performance PCIe 5.0 SSD for Enterprise Servers, su news.samsung.com. URL consultato l'8 gennaio 2022.

- ^ (EN) PCI-SIG® Announces Upcoming PCI Express® 6.0 Specification to Reach 64 GT/s, su businesswire.com, 18 giugno 2019. URL consultato l'8 gennaio 2022.

- ^ (EN) PCI Express 7.0 Specification Announced - Hitting 128 GB/s In 2025, su www.phoronix.com. URL consultato il 21 giugno 2022.

Bibliografia

modifica- Andrew Stuart Tanenbaum, PCI Express, in Architettura dei calcolatori. Un approccio strutturale, Milano, Pearson Education, 2006, pp. 206-210, ISBN 978-88-7192-271-3.

Voci correlate

modificaAltri progetti

modifica- Wikimedia Commons contiene immagini o altri file su PCI Express

Collegamenti esterni

modifica- (EN) Specifiche PCI Express, su pcisig.com.

- (EN) Sito di sviluppo Intel per l'architettura PCI Express, su intel.com.

- (EN) PCI Express: Un'anteprima, su arstechnica.com.

- (EN) Risorse per progettisti di sistemi PCI Express, su eurekatech.com. URL consultato il 18 luglio 2006 (archiviato dall'url originale il 28 giugno 2006).

- (EN) Form-Factors PCI Express, su rtcmagazine.com (archiviato dall'url originale il 10 agosto 2006).

- (EN) pinout PCI Express, su pinouts.ru.

- (EN) IDT + PCI Express solutions, su idt.com.

- PCI Express sotto analisi: velocità a confronto, su tomshw.it. URL consultato il 16 luglio 2007 (archiviato dall'url originale il 1º luglio 2007).